PolyFiX Level control

M.Torres, Nov 2012 rev Jun 2013

1. Master level "tweak" loop

The digitizer chip is driven by a 0-4GHz, differential Variable Gain Amplifier (VGA). Its gain control curve is fairly linear from 4dB@Vg=0.8V to 20dB@Vg= -2.3V. This voltage range is swept by a 10-bit DAC , so one LSB corresponds to a 0.016 dB gain change.

| signal weak | signal nominal | signal strong | |

| Signal strength/nominal | -10dB | 0dB | +6dB |

| DAC value | 0 | 625 | 1023 |

| VGA gain | 20dB | 10dB | 4dB |

| dB / step | 0.016 | 0.016 | 0.016 |

The computer reads the Total Power Detector (TPD) and writes the DAC. After a few iterations the loop converges to a predefined TPD level.

The value from the TPD is fluctuating due to noise. Consecutive program runs should statistically provide the same result with a deviation not causing the DAC value to change by more than a few LSB steps. In 31msec, 256 million samples are available to the TPD. The corresponding relative fluctuation is 1/16000, which is more than necessary. This suggests that some decimation can be practiced to save PGA resource. A decimation factor of 1/64 leads to a 1/2000 fluctuation, which is adequate for a stable result.

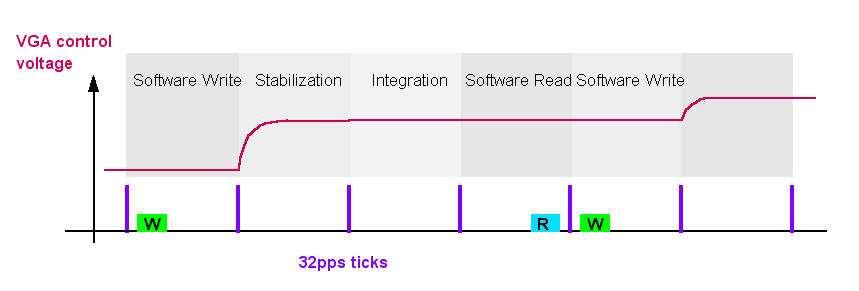

The software Write is applied to the hardware at the next 32pps tick. The gain control voltage needs a few milliseconds to establish, during which total power can't be integrated. After a tick the data integrated during the previous period is transmitted to the computer, which sends the new value. So an iteration cycle requires four 31msec periods.

The total time for the tweak loop to converge depends on the algorithm performance. Less than one second (~7 iterations) is expected. After this is done, the computer initiates the :

2. Sub-band level "equalizer" loop

The gains of the 64 primary channels are individually adjusted by a similar servo loop, except that its sensor and actuator are of different nature.

- The total power of each primary channel is sensed by adding all the secondary channels of its auto-spectrum in the computer.

- The variable gain element is a digital multiplier, whose multiplicand is a number proportional to signal voltage.

| signal weak | signal nominal |

signal strong | |

| Signal strength/nominal | -6dB | 0dB | +6dB |

| Gain register value | 1024 | 512 | 256 |

| Multiplier coefficient | 2.0 | 1.0 | 0.5 |

| dB / step | 0.009 | 0.017 | 0.034 |

Regarding fluctuation, there are 4 million samples available in a 31msec period. This gives a 1/2000 fluctuation of the power measurement, which is sufficiently averaged to address a 10-bit register.

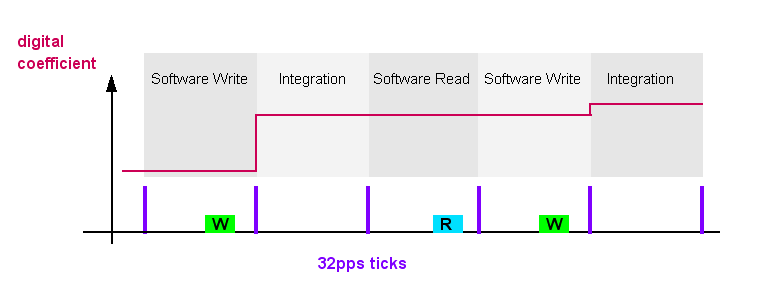

The digital multiplier has zero settling time. Then the equalizer loop can consist of only three periods of 31msec. Convergence is reached slighly faster than the masterlevel loop.

3. Conclusion

The two leveling loops require similar, but differently optimized softwares. The whole tweak process of a PolyFiX unit should take less than 2 seconds. When finished, it would be very helpful for IF transmission troubleshooting to return to the operator console 12 small images (e.g. 64x32) representing the spectra of the 0-4 GHz inputs, expressed in dB/ nominal level.